本帖最后由 广州创龙廖工 于 2017-2-10 15:16 编辑

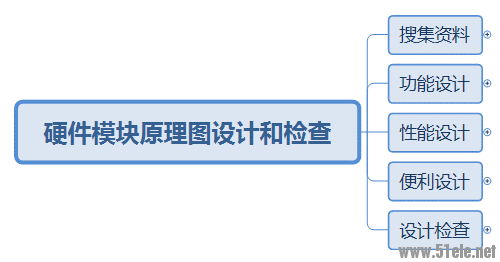

这里提到的硬件设计主要指基于芯片级的外围电路设计。这次总结以MicroChip的一个网口PHY芯片KSZ9031MNX的设计为例来讲解。

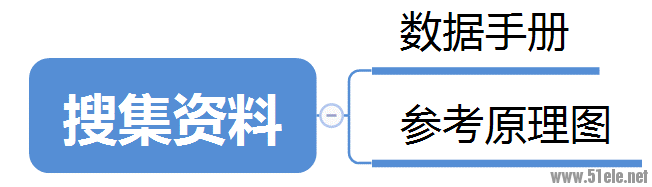

第一步:搜集资料

参考资料可以从官网、搜索引擎获取,当然能拿到已经验证的那就几乎搞定了原理图设计。

官网资料搜索: http://www.microchip.com/search/ ... x?id=2&q=KSZ9031MNX

参考板资料: http://www.microchip.com/Develop ... tNO=KSZ9031MNX-EVAL

找到数据手册后,先整体阅读数据手册,明确芯片功能,原理框图,有无特别注意事项等。

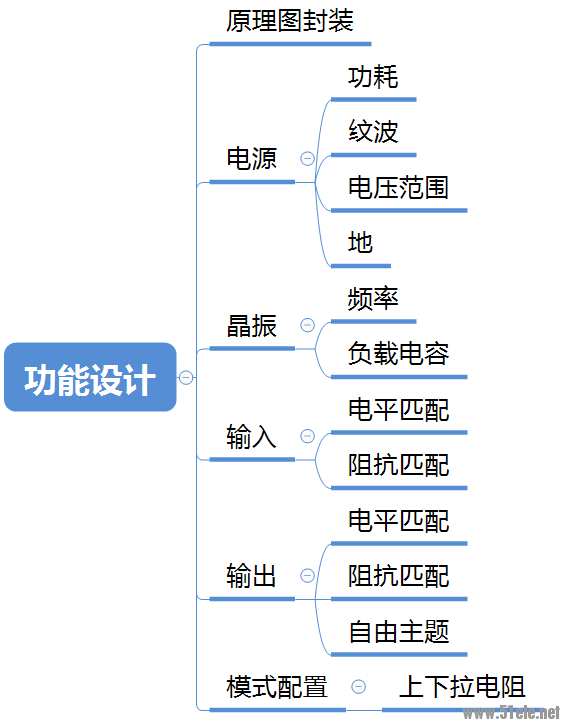

第二步:功能设计

l 拿到参考资料后,开始设计,首先确定器件的唯一型号,确定并绘制原理图封装,绘制完后记得按照引脚列表进行double check。对于一个引脚描述的理解错误可以导致芯片乃至一个设备的损坏。 l 按照芯片给出的电气特性----Operating Ratings,进行电源设计,评估各路电源电压值、最大电流值、波动范围,选取合适的DCDC或LDO。 l 按照手册描述,确定晶振频率,是有源还是无源,如果是无源,需计算出负载电容的大小。 l 输入端,首先看接口是否吻合,GMII肯定得对GMII的接口才行,电平不能搞错了,比如有时会出现处理器的电平是3.3V的但是PHY的电平是2.5V的,这时候,如果PHY不兼容3.3V的话,就需要增加电平转换芯片了。

除了电平,也要考虑输入端的信号线阻抗要求,参考下一点的RJ的RX端。 l 输出端,和输入端类似,这里的PHY的输出端有两个,一边是连接处理那边的RX,另外一边是连接RJ45的TX,连接RJ45那端就需要考虑阻抗匹配了,网口是100欧姆的差分对阻抗。 l 然后是模式配置,这个案例中包括LED模式、地址、PHY工作模式、125MHz时钟输出等配置。 LED使用RJ45自带LED,选择为单LED灯模式,而非选用可以显示三种颜色的双LED灯模式。 使用10K下拉电阻配置地址为00000,配置地址时需注意,如果一个板子上有两个电阻,记得配置为不同的地址。 使用的是GMII,这里配置为0001模式。 配置为125MHz使能输出,实际设计并未使用到该信号,这个125MHz是用来作为KSZ9031MNX正常供电已经跑起来的标志。

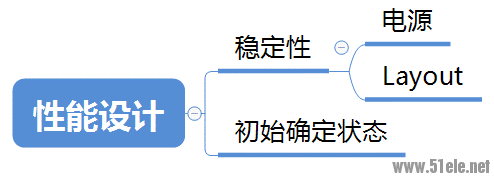

按照上面这几个步骤,结合原理图引脚说明及其对应细节部分,基本上就可以搭建一个芯片外围电阻的原始稿了,使用软件自带的DRC功能检查修改后,接下来就是优化工作了。 第三步:性能设计

优化工作,主要是从稳定性和确定初始状态上着手。稳定性,比如这个PHY芯片官方的方案的1.25V的电源是使用PHY芯片自带控制引脚控制MOS管产生1.25V的电源,但是这种方式,一不注意,控制线受到时钟线、晶振的影响,导致电源偏离芯片正常工作范围。此类敏感部分,可以考虑使用1.2V的LDO替代,保证其电压不偏离。另外是初始状态的确定,比如复位、LED灯等,需要在芯片上电完成之前给予一个确定状态,比如LED如果没有确定状态,芯片初始化完成之前可能LED灯会微微发亮。 补充一点就是注意BOM的排查,比如成本、供货情况等。

|  |手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )

|手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )