|

創龍工程師, 您好: 我購買TL138 EthEVM-A2 開發板, 目前用 demo code 雙核通訊都可正常運行, 經由DSP控制 EMIFA 使用CS2與外部FPGA做資料連結. 使用光碟所提供的 EMIFA_FPGA 代碼, 目前外部是空接用LA分析其 EMIF 發送的資料, 發現一個奇怪的問題! 1. 外部空接情況, 不論資料如何發送(0x0001 or 0x1ffff), 其D0 一直保持為低電壓; 2. D0外部上拉1K電阻後, 不論資料如何發送(0x0000), 其D0 一直保持為高電壓;

( s7 W7 Y% G1 e- ^, z. J

其餘 bus (D15 ~ D1), CS2, R/W, WE... 可正常控制, 唯有D0 !? 8 D5 n# Q' k$ |6 b, f5 J4 ]

因為是參考創龍提供的源碼, 也試過調整時序(write-setup, strobe,hold/ Read-setup, strobe, hold) 幫助不大; 回讀PLLDIV3(0x01E1A120) =0x8003, 表示EMIF Clock 為114MHz 9 b( C% r8 I2 X0 W

void EMIFInit(void) { //配置EMIFA相關复用引腳 EMIFAPinMuxSetup(); //配置數據總線16bit EMIFAAsyncDevDataBusWidthSelect(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_2, EMIFA_DATA_BUSWITTH_16BIT); //選擇 Normal 模式 EMIFAAsyncDevOpModeSelect(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_2, EMIFA_ASYNC_INTERFACE_NORMAL_MODE); //禁止 WAIT 引腳 EMIFAExtendedWaitConfig(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_2, EMIFA_EXTENDED_WAIT_DISABLE); //配置 W_SETUP/R_SETUP W_STROBE/R_STROBE W_HOLD/R_HOLD TA 等參數 EMIFAWaitTimingConfig(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_2, EMIFA_ASYNC_WAITTIME_CONFIG(1, 2, 1, 1, 2, 1, 0 )); }

1 E/ v1 c2 W. G7 J4 r: n6 V' b

) M$ H ^- c9 |9 N+ d

. V$ q3 N4 [3 n& \2 t9 b, u

7 U; k# U! K- v) J8 G

|

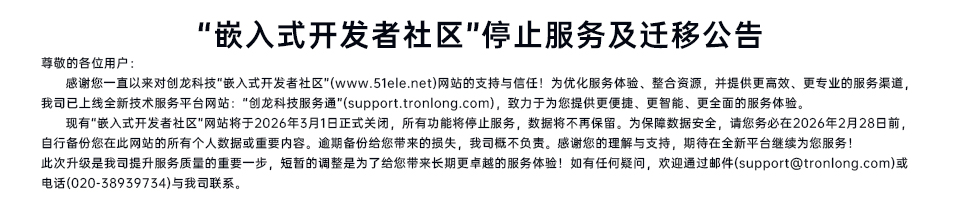

|手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )

|手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )