|

|

8#

楼主 |

发表于 2018-11-10 16:06:15

|

只看该作者

/ ?* p5 C" O W

采用的OMAP-L138F上ARM与FPGA数据传输程序基于文件《13-3-OMAPL138基于EMIFA总线与FPGA的通信测试》。1 H# B, f' c) ~; {3 z3 X

/ v! ^8 o) R6 @5 `

现在遇到的问题:8 h. P) |% h- ?

1、16bit数据线高八位没有初始化,传输只采用低八位数据线,且16bit的数据会在低八位数据线分成两个8bit数发出;

4 U7 q3 ]$ Z1 Q" S& j! e! f8 V2、地址线仅有低三位初始化,且变化方式与读使能不同步;emifa_ba1无变化;' H( l" N: z( c+ ^7 L% d1 o

- A* f2 l$ a% R0 D, O9 ^9 W现象:. a7 b& z) k' C( a9 @2 [9 m9 t

1、linux端运行./tl-devmem2 0x60000000 256 m 52428(1100110011001100)FPGA端现象6 c* e( G; `; D! \* m8 _& R# Y* b+ {

G:\EMIF问题\输入(m52428)

/ f$ O2 d. t! s+ U, LG:\EMIF问题\m52428addr

6 T3 l$ ?) f: n# n# E. W2、linux端运行./tl-devmem2 0x60000000 256 h 52428(1100110011001100)FPGA端现象( e2 r7 Y6 B1 m

G:\EMIF问题\输入(h52428)G:\EMIF问题\h52428addr1 v" b( O6 [6 D5 b8 q; U. D

|

|

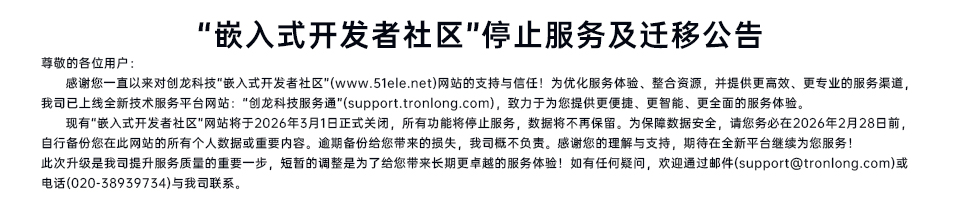

|手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )

|手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )