|

|

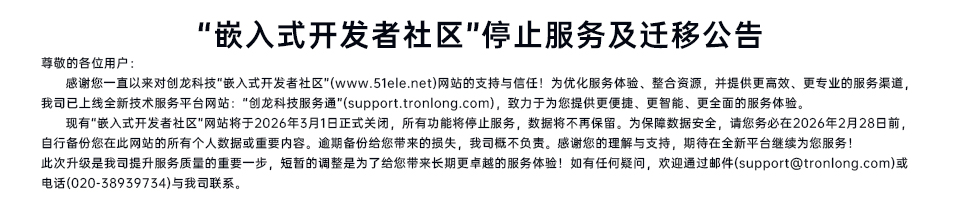

硬件平台:omapl38F核心板;' ?9 Z `8 h0 G: W [+ D/ K& `, X

复现方式:按照pdf:omapl38基于emifa总线与FPGA的通信测试进行例程复现,并将写数据部分提取出来进行使用;

/ e) z. h# K: P) ~6 G' J7 Y问题:在对fpga这边数据进行抓包观察时发现:

k+ D% ]8 f$ j) w1、16根数据线仅有低八位在使用,高八位置一,当传输16bit数据时,会将两个字节按先小端后大端的顺序从低八位数据线按序输出;

' B" R/ j1 q! z; r2、同时地址线只有addr1,addr2,addr3三根是有效的,其他线长期置一,并且地址线并不随数据变化而变化,而是每隔8到11个写使能而进一位;, D$ T! X" R" x+ |6 E, d

3、emifa_clk时钟线并不能作为时钟提供给fpga,在对fpga另加其他时钟并对emifa_clk进行抓包时现象为长期置高;

2 e) L5 T2 q @0 `7 _% a! i4、片选emifa_cs2和写使能emifa_we的拉低时间比并不符合dsp与fpga通信时的2,3,2关系,请问arm与fpga通信时这个时序是什么,同时其依靠的时钟是多大,还是114MHz吗?

) A8 b' S0 y% @ r) S" K |

本帖子中包含更多资源

您需要 登录 才可以下载或查看,没有帐号?立即注册

x

|

|手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )

|手机版|小黑屋|嵌入式开发者社区

( 粤ICP备15055271号 )